PCI-4 July 15, 2004

# **Product Specification for Model PCI-4**

The Model PCI-4 is a PCI bus form factor and bus compatible module that provides four channels of magnetostrictive transducer interface. When commanded by the PC, the module interrogates the transducers and converts the timing information to position values. The module can be configured to operate with Start/Stop, Trailing Edge Start/Stop, Pulse Width Modulated or SSI transducers. Each Start/Stop channel can support one to thirty one recirculations or from one to thirty one magnets. All operations are controlled by the host PC software. A 56 MHz oscillator provides excellent resolution; 0.002 inches using one recirculation or in the multi-magnet mode. The transducers are electrically isolated from the PC power supply. Transducer connections are made via a 37 pin DSUB connector on the rear of the board. Transducer power can be brought to the board on a two-position screw terminal connector where it is distributed to the J1 connector.

### **FEATURES**

- PCI Plug and Play operation with no dipswitches to set.

- Supports from 1 to 4 magnetostrictive transducers

- Can be configured with any combination of Start/Stop, Pulse Width Modulated or SSI transducers

- 56 MHz Count oscillator provides 0.001 inch resolution with 2 recirculations

- 24 bit position counter for each transducer

- 24 or 25 bit SSI position

- Number of recirculations or magnets software selectable from 1 to 15

- Multiple magnet mode measures from 1 to 31 magnets on each of the transducers

- Optical isolation between the transducer and the board to prevent damage to PC

- Cables directly to the transducer

- The 24V transducer power can be distributed by the board

- Separate 2 pin screw terminal for +24V transducer power

- Individual status registers provides ready indication for each channel

- Half length PCI board is 5.2 inches long

# Rapid Controls Inc.

Box 8390 • Rapid City, SD • 57709 Phone: 605-348-7688 • Fax: 605-341-5496

http://www.rapidcontrols.com/ • email: info@rapidcontrols.com

PCI-4 July 15, 2004

#### **SPECIFICATIONS**

- PCI 2.1 compatible

- 56 MHz oscillator provides 0.001 inch resolution with 2 recirculations

- Multi-magnet mode requires Start Stop transducer and must be interrogated once for each magnet

- Magnet number in Multi-magnet mode is software settable from 1 to 31

- 37 pin DSUB connector to the transducers

- Transducer I/O is RS422 compatible

- The Gate transducer inputs to the board are terminated in 120 ohms

- Re-circulations are software settable from 1 to 31.

- Requires an externally interrogated transducer for PWM operation

- Occupies 16 bytes of I/O space

- Power Requirements: 5 VDC @ < 500 ma.</li>

- Size: 5.2 x 4.2 inch (132 x 107 mm).

### Model numbering

Specify Model: **PCI-4-***ABCD*

A - Channel A type

**B** - Channel B type

*C* - Channel C type

D - Channel D type

Substitute one of the following for the channel type:

**R** - Leading Edge Start/Stop or PWM\*

S - SSI

T - Trailing Edge Start/Stop or PWM\*

N - None

For example, a board with two start/stop interfaces on channels A and B and two SSI transducers on channels C and D would be model PCI-4-RRSS.

\*PWM operation requires an externally interrogated PWM transducer.

PCI-4 July 15, 2004

| I | Insta | allation                                                 | . 1 |

|---|-------|----------------------------------------------------------|-----|

|   | 1.1   | Overview                                                 | . 1 |

|   | 1.2   | Installing the board                                     | . 1 |

|   | 1.2.  | 1 Windows 98 Driver Installation                         | . 1 |

|   | 1.2.  | Windows NT 4.0 Driver Installation                       | . 1 |

|   | 1.2.  | 3 Windows 2000 Driver Installation                       | . 1 |

|   | 1.2.  | 4 SDK Installation                                       | . 2 |

|   | 1.2.  | 5 Dos Installation                                       | . 2 |

| 2 | The   | ory of operation                                         | . 2 |

|   | 2.1   | Board functions and addressing                           | . 2 |

|   | 2.1.  | 1 Address decoding                                       | . 2 |

|   | 2.1.2 | 2 I/O map                                                | . 2 |

|   | 2.2   | Start/Stop, PWM transducers                              |     |

|   | 2.3   | Channel Registers (base +0, +1, +2) for all channels     | . 3 |

|   | 2.3.  |                                                          |     |

|   | 2.4   | SSI transducers                                          | . 5 |

|   | 2.4.  | Programming (SSI), Data Registers                        | . 5 |

|   | 2.4.2 | Programming (SSI), Command / Status Registers (Base + 3) | . 5 |

| 3 | Jum   | pers                                                     | 6   |

|   | 3.1   | Jumper map                                               | 6   |

|   | 3.2   | Jumpers X1 through X4 (Factory Set)                      | 6   |

| 4 | Con   | nections                                                 | 7   |

|   | 4.1   | J1, 32 bit PCI bus connector, required.                  | 7   |

|   | 4.2   | P2, Thirty seven pin DSUB transducer connector.          | 7   |

|   | 4.3   | P1, Two position screw terminal                          | 7   |

|   | 4.4   | Optional cable termination.                              | . 8 |

PCI-4 1 July 15, 20044

### 1 Installation

#### 1.1 Overview

The installation consists of two portions, the driver install and the SDK install. The driver install installs a driver that allows Windows applications to access the PCI4 hardware. The SDK install installs the DLLs and header files that provide an API allowing programs to use the PCI4 easily. See the PCI4 SDK Programmer's Reference for more information. The Windows NT installation combines these steps.

Note that the PCI4 is a Plug and Play device and has no jumpers to be set. The Plug and Play Bios will automatically assign the PCI4 an address space.

#### 1.2 Installing the board

Install the PCI4 in an unused PCI slot. If you are using Windows 98, proceed to section 1.2.1. If you are using Windows NT, proceed to section 1.2.2. If you are using Windows 2000, proceed to section 1.2.3. Currently the PCI4 is not supported in Windows 95 or Windows ME. No special installation is required for DOS applications.

#### 1.2.1 Windows 98 Driver Installation

After booting for the first time with the PCI4 installed, Windows will detect the PCI4 as an unknown PCI device. If this does not happen, use the Add New Hardware applet from the control panel.

- 1. After detection, the search for drivers dialog will open. Select "Next".

- 2. Select "Search for a suitable driver" and press "Next".

- 3. Uncheck all choices except "Specify a location". Enter the location of the PCI-4 SDK CD (e.g. D:\) and press "Next".

- 4. Windows should find the correct driver at this point. Press "Next". If Windows cannot locate the driver, check that the location entered in step 4 is correct.

- 5. Press finish after Windows installs the driver.

Continue with section 1.2.4.

#### 1.2.2 Windows NT 4.0 Driver Installation

Skip to section 1.2.4. Setup.exe will install the drivers necessary for Windows NT.

#### 1.2.3 Windows 2000 Driver Installation

After booting for the first time with the PCI4 installed, Windows will detect the PCI4 as an unknown PCI device. If this does not happen, use the Add/Remove Hardware applet from the control panel.

- 1. After detection, the search for drivers wizard will open. Select "Next".

- 2. Select "Search for a suitable driver" and press "Next".

- 3. Uncheck all choices except "Specify a location". Select "Next".

- 4. Enter the location of the PCI-4 SDK CD (e.g. D:\) and select "OK".

# Rapid Controls Inc.

- 5. Windows should find the correct driver at this point. Press "Next". If Windows cannot locate the driver, check the location entered in step 4 is correct.

- 6. Press finish after Windows installs the driver.

Continue with section 1.2.4.

#### 1.2.4 SDK Installation

Run setup.exe from the installation CD. This will install the PCI4 SDK and DLLs. The SDK files are installed to C:\pci4 (or x:\pci4 where x is the boot drive letter, if the boot drive is not C.) Reboot the computer before attempting to use the PCI4 SDK.

#### 1.2.5 Dos Installation

There is no special procedure for DOS installation. The files in the SDKFiles directory of the PCI4 CD can be copied to the hard drive for use.

### 2 Theory of operation

#### 2.1 Board functions and addressing

The board is comprised of five logical sections, the PCI section and a Rapid Controls EPLD for each channel. The PCI9052 interface chips reads its' setup information from the 93LC46B EEPROM which is factory programmed.

#### 2.1.1 Address decoding

The setup from the EEPROM defines the local bus space as 16 bytes of I/O. Address decoding is provided by the PCL9052 PCI interface chip. When the board is installed the operating system or Bios assigns an address to the board. All access to the four transducer interfaces must be through the address space provided by the PCI Bios.

#### 2.1.2 I/O map

The PCI-4 board occupies 16 bytes of I/O space, the base address of which is assigned by the motherboard's PCI controller. The I/O map is divided into four 4 byte sections. Channel 1 occupies the first four bytes, channel 2 the next four etc.

| Address    | Function        | $2^{0}$  | $2^{1}$        | $2^{2}$  | $2^3$    | $2^{4}$  | $2^{5}$  | $2^{6}$  | $2^{7}$  |

|------------|-----------------|----------|----------------|----------|----------|----------|----------|----------|----------|

| Base + 0   | Rd transducer 1 | Data     | Data           | Data     | Data     | Data     | Data     | Data     | Data     |

|            | data low byte   | $2^{0}$  | 2 <sup>1</sup> | $2^2$    | $2^3$    | $2^4$    | $2^{5}$  | $2^{6}$  | 27       |

| Base + 1   | Rd transducer 1 | Data     | Data           | Data     | Data     | Data     | Data     | Data     | Data     |

|            | data mid byte   | 28       | 29             | $2^{10}$ | $2^{11}$ | $2^{12}$ | $2^{13}$ | $2^{14}$ | $2^{15}$ |

| Base $+2$  | Rd transducer 1 | Data     | Data           | Data     | Data     | Data     | Data     | Data     | Data     |

|            | data high byte  | $2^{16}$ | $2^{17}$       | $2^{18}$ | $2^{19}$ | $2^{20}$ | $2^{21}$ | $2^{22}$ | $2^{23}$ |

| Base $+3$  | Rd transducer 1 | See      |                |          |          |          |          |          |          |

|            | status          | section  |                |          |          |          |          |          |          |

| Base $+ 3$ | Wr transducer 1 | See      |                |          |          |          |          |          |          |

|            | command         | section  |                |          |          |          |          |          |          |

| Base + 4   | Rd transducer 2 | Data     | Data           | Data     | Data     | Data     | Data     | Data     | Data     |

|            | data low byte   | $2^{0}$  | $2^{1}$        | $2^{2}$  | $2^{3}$  | $2^{4}$  | $2^{5}$  | $2^{6}$  | $2^{7}$  |

| Base + 5   | Rd transducer 2 | Data     | Data           | Data     | Data     | Data     | Data     | Data     | Data     |

|            | data mid byte   | $2^{8}$  | 29             | $2^{10}$ | $2^{11}$ | $2^{12}$ | $2^{13}$ | $2^{14}$ | $2^{15}$ |

| Base + 6   | Rd transducer 2 | Data     |

|------------|-----------------|----------|----------|----------|----------|----------|----------|----------|----------|

|            | data high byte  | $2^{16}$ | $2^{17}$ | $2^{18}$ | $2^{19}$ | $2^{20}$ | $2^{21}$ | $2^{22}$ | $2^{23}$ |

| Base $+7$  | Rd transducer 2 | See      |          |          |          |          |          |          |          |

|            | status          | section  |          |          |          |          |          |          |          |

| Base $+7$  | Wr transducer 2 | See      |          |          |          |          |          |          |          |

|            | command         | section  |          |          |          |          |          |          |          |

| Base + 8   | Rd transducer 3 | Data     |

|            | data low byte   | $2^{0}$  | $2^1$    | $2^{2}$  | $2^{3}$  | $2^{4}$  | $2^{5}$  | $2^{6}$  | $2^{7}$  |

| Base $+ 9$ | Rd transducer 3 | Data     |

|            | data mid byte   | $2^{8}$  | $2^{9}$  | $2^{10}$ | $2^{11}$ | $2^{12}$ | $2^{13}$ | $2^{14}$ | $2^{15}$ |

| Base + 10  | Rd transducer 3 | Data     |

|            | data high byte  | $2^{16}$ | $2^{17}$ | $2^{18}$ | $2^{19}$ | $2^{20}$ | $2^{21}$ | $2^{22}$ | $2^{23}$ |

| Base + 11  | Rd transducer 3 | See      |          |          |          |          |          |          |          |

|            | status          | section  |          |          |          |          |          |          |          |

| Base +11   | Wr transducer 3 | See      |          |          |          |          |          |          |          |

|            | command         | section  |          |          |          |          |          |          |          |

| Base + 12  | Rd transducer 4 | Data     |

|            | data low byte   | $2^{0}$  | $2^1$    | $2^2$    | $2^{3}$  | $2^{4}$  | $2^{5}$  | $2^{6}$  | 27       |

| Base + 13  | Rd transducer 4 | Data     |

|            | data mid byte   | $2^{8}$  | $2^{9}$  | $2^{10}$ | $2^{11}$ | $2^{12}$ | $2^{13}$ | $2^{14}$ | $2^{15}$ |

| Base + 14  | Rd transducer 4 | Data     |

|            | data high byte  | $2^{16}$ | $2^{17}$ | $2^{18}$ | $2^{19}$ | $2^{20}$ | $2^{21}$ | $2^{22}$ | $2^{23}$ |

| Base + 15  | Rd transducer 4 | See      |          |          |          |          |          |          |          |

|            | status          | section  |          |          |          |          |          |          |          |

| Base + 15  | Wr transducer 4 | See      |          |          |          |          |          |          |          |

|            | command         | section  |          |          |          |          |          |          |          |

#### 2.2 Start/Stop, PWM transducers

The host PC104 processor writes a recirculation value and mode to the Control/Status register, loading the recirculation count. The control register write causes an interrogation pulse to be issued from the EPLD which in turn causes a 1 microsecond pulse to be issued from the Interrogate + and - outputs of the board. The transducer immediately responds with a 1 microsecond Gate + and - pulse. This pulse increments the recirculation register and starts the position counter counting. After the time required for the torque pulse to propagate down the transducer from the magnet (9 \* inches microseconds) another Gate + and Gate - pulse is returned from the transducer. This again increments the recirculation counter. If it is not the last recirculation another one microsecond interrogate pulse is issued. This process continues until the last interrogation when the last Gate+ and Gate - pulse returned stops the position counter and sets the process completed flag. The 24 bit counter can now be read and will hold a value of (inches \* Gradient \* 56 \* recirculations).

When operating in the PWM mode the counter counts from the leading edge to the trailing edge of the Gate pulse. The multi-magnet mode functions the same as the recirculation mode except that only one interrogate pulse is issued. The magnet measured is determined by the recirculation count programmed. Since only a single magnet can be measured at one time, the transducer must be interrogated once for each new magnet position desired. The software must wait each time for all of the magnets to respond, this is best accomplished by waiting a time equal to 9\* (length of the transducer + 10) microseconds between interrogations.

### 2.3 Channel Registers (base +0, +1, +2) for all channels

|      | $2^{0}$             | 21                  | $2^2$               | $2^3$               | $2^4$               | $2^5$               | $2^{6}$             | $2^7$               |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Read | Data 2 <sup>0</sup> | Data 2 <sup>1</sup> | Data 2 <sup>2</sup> | Data 2 <sup>3</sup> | Data 2 <sup>4</sup> | Data 2 <sup>5</sup> | Data 2 <sup>6</sup> | Data 2 <sup>7</sup> |

PCI-4 4 July 15, 20044

| Base + 0   |                      |                      |                      |                      |                      |                      |                      |                      |

|------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Read       | Data 2 <sup>8</sup>  | Data 2 <sup>9</sup>  | Data 2 <sup>10</sup> | Data 2 <sup>11</sup> | Data 2 <sup>12</sup> | Data 2 <sup>13</sup> | Data 2 <sup>14</sup> | Data 2 <sup>15</sup> |

| Base $+ 1$ |                      |                      |                      |                      |                      |                      |                      |                      |

| Read       | Data 2 <sup>16</sup> | Data 2 <sup>17</sup> | Data 2 <sup>18</sup> | Data 2 <sup>19</sup> | Data 2 <sup>20</sup> | Data 2 <sup>21</sup> | Data 2 <sup>22</sup> | Data 2 <sup>23</sup> |

| Base $+2$  |                      |                      |                      |                      |                      |                      |                      |                      |

### 2.3.1 Programming (Start/Stop and PWM), Command Data Register (base + 3)

|          | $2^{0}$                | 21                     | $2^2$                  | $2^3$                  | $2^4$                  | $2^{5}$ | $2^{6}$ | $2^{7}$   |

|----------|------------------------|------------------------|------------------------|------------------------|------------------------|---------|---------|-----------|

| Write    | Recircs 2 <sup>0</sup> | Recircs 2 <sup>1</sup> | Recircs 2 <sup>2</sup> | Recircs 2 <sup>3</sup> | Recircs 2 <sup>4</sup> | PWM     | Multi   | Interrupt |

| Command  |                        |                        |                        |                        |                        | Mode    | magnet  | Enable    |

| Base + 3 |                        |                        |                        |                        |                        |         | Mode    |           |

| Read     | Recircs 2 <sup>0</sup> | Recircs 2 <sup>1</sup> | Recircs 2 <sup>2</sup> | Recircs 2 <sup>3</sup> | Recircs 2 <sup>4</sup> | PWM     | Multi   | Data      |

| Status   |                        |                        |                        |                        |                        | Mode    | magnet  | Ready     |

| Base + 3 |                        |                        |                        |                        |                        |         | Mode    |           |

The PWM mode bit should be set to 1 for PWM transducers and 0 for Start Stop.

The Multi-magnet bit should be set to 1 for multi magnet operation and 0 for single magnet operation. The PWM and Multi-magnet bits are mutually exclusive. Setting them both to 1 will lead to undefined results.

http://www.rapidcontrols.com/ • email: info@rapidcontrols.com

#### 2.4 SSI transducers

The host PC processor writes a bit length value to the Control/Status register causing the clock generator to start the clock data process. The board generates the proper number of clock pulses at 218 KHz and clocks in the data response from the transducer. When all 24 or 25 bits have been clocked into the registers the data ready flag is set. If interrupts were enabled the interrupt line is driven high. Data is available in the four registers. The transducer controls the resolution and data format, Gray code or binary.

### 2.4.1 Programming (SSI), Data Registers

|            | $2^{0}$              | 21                   | $2^2$                | $2^3$                | $2^4$                | $2^{5}$              | $2^{6}$              | 27                   |

|------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Read       | Data 2 <sup>0</sup>  | Data 2 <sup>1</sup>  | Data 2 <sup>2</sup>  | Data 2 <sup>3</sup>  | Data 2 <sup>4</sup>  | Data 2 <sup>5</sup>  | Data 2 <sup>6</sup>  | Data 2 <sup>7</sup>  |

| Base $+ 0$ |                      |                      |                      |                      |                      |                      |                      |                      |

| Read       | Data 2 <sup>8</sup>  | Data 2 <sup>9</sup>  | Data 2 <sup>10</sup> | Data 2 <sup>11</sup> | Data 2 <sup>12</sup> | Data 2 <sup>13</sup> | Data 2 <sup>14</sup> | Data 2 <sup>15</sup> |

| Base $+ 1$ |                      |                      |                      |                      |                      |                      |                      |                      |

| Read       | Data 2 <sup>16</sup> | Data 2 <sup>17</sup> | Data 2 <sup>18</sup> | Data 2 <sup>19</sup> | Data 2 <sup>20</sup> | Data 2 <sup>21</sup> | Data 2 <sup>22</sup> | Data 2 <sup>23</sup> |

| Base $+2$  |                      |                      |                      |                      |                      |                      |                      |                      |

#### 2.4.2 Programming (SSI), Command / Status Registers (Base + 3)

|           | 20                   | 21  | $2^2$ | $2^3$ | $2^4$ | $2^{5}$    | $2^{6}$ | $2^7$     |

|-----------|----------------------|-----|-------|-------|-------|------------|---------|-----------|

| Write     | N/A                  | N/A | N/A   | N/A   | N/A   | Set for 25 | N/A     | Interrupt |

| Command   |                      |     |       |       |       | bit. Clear |         | Enable    |

| Base $+3$ |                      |     |       |       |       | for 24 bit |         |           |

| Read      | Data 2 <sup>24</sup> | 0   | 0     | 0     | 0     | 0          | N/A     | Data      |

| Status    |                      |     |       |       |       |            |         | Ready     |

| Base + 3  |                      |     |       |       |       |            |         |           |

# 3 Jumpers

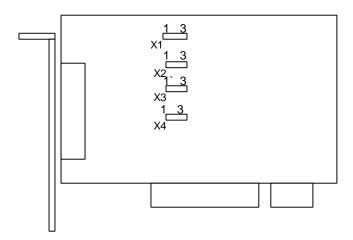

### 3.1 Jumper map

# 3.2 Jumpers X1 through X4 (Factory Set)

Jumpers X1 through X4 are factory set and must be set according to the type of transducer connected to channel A through F respectively. Connect 1 to 2 for Start/Stop and PWM type transducer. Connect 2 to 3 for SSI transducers.

### 4 Connections

# 4.1 J1, 32 bit PCI bus connector, required.

### 4.2 P2, Thirty seven pin DSUB transducer connector.

| 1  | Gate A -          | 20 | Gate A +         |

|----|-------------------|----|------------------|

| 2  | Interrogate A+    | 21 | Interrogate A -  |

| 3  | Transducer ground | 22 | Transducer Power |

| 4  | Gate B -          | 23 | Gate B +         |

| 5  | Interrogate B +   | 24 | Interrogate B -  |

| 6  | Transducer ground | 25 | Transducer Power |

| 7  | Gate C -          | 26 | Gate C +         |

| 8  | Interrogate C +   | 27 | Interrogate C -  |

| 9  | Transducer ground | 28 | Transducer Power |

| 10 | Gate D -          | 29 | Gate D +         |

| 11 | Interrogate D +   | 30 | Interrogate D -  |

| 12 | Transducer ground | 31 | Transducer Power |

| 13 |                   | 32 |                  |

| 14 |                   | 33 |                  |

| 15 | Transducer ground | 34 | Transducer Power |

| 16 |                   | 35 |                  |

| 17 |                   | 36 | -                |

| 18 | Transducer ground | 37 | Transducer Power |

| 19 | Transducer ground |    |                  |

Transducer power on pins 22, 25, 28, 31, 34 and 37 is not required by the PC4-TEMPO board but can be used to connect the + voltage from P1, pin 1 to the transducer (Red).

# 4.3 P1, Two position screw terminal

| 1 | + Transducer power input |

|---|--------------------------|

| 2 | - Transducer ground      |

Transducer power can be supplied to the transducers via P1 pin 1. A diode prevents accidentally applying a negative voltage to the transducers. Transducer ground is connected via P1 pin 2.

# 4.4 Optional cable termination

Rapid Controls can provide Model CAB-TERM37 which provides a 10 ft cable and a screw terminal board. This allows connecting wires to the PCI-4 via a screw terminal rather than creating a cable. Pin numbering on the screw terminals is the same as the P2 connector defined above.

http://www.rapidcontrols.com/ • email: info@rapidcontrols.com